博通公司昨日宣布了一项重大技术创新,推出了业界首个3.5D F2F封装技术平台——3.5D XDSiP。该平台专为满足大型人工智能(AI)芯片对高性能与低功耗的双重需求而设计,能够在单一封装中集成超过6000平方毫米的硅芯片以及多达12个HBM内存堆栈。

3.5D XDSiP平台不仅超越了传统的2.5D封装技术,还实现了上下两层芯片顶部金属层的直接连接,即3D混合铜键合技术。这一创新不仅提供了最小的电气干扰,还确保了卓越的机械强度,为芯片封装领域树立了新的标杆。

与传统的“面对背”式芯片垂直堆叠相比,3.5D XDSiP平台采用的“面对面”连接方式拥有高达7倍的信号密度。这一设计最大限度地减少了3D芯片堆栈中各组件间的延迟,并将平面芯片间PHY接口的功耗降低了九成。3.5D XDSiP平台还实现了更小的中介层和封装尺寸,从而在降低成本的同时,有效改善了大面积封装可能遇到的翘曲问题。

博通公司高级副总裁兼ASIC产品部总经理Frank Ostojic表示,随着摩尔定律的极限逐渐显现,先进的封装技术对于下一代XPU集群的发展至关重要。通过与客户的紧密合作,并在台积电和EDA合作伙伴的技术与工具支持下,博通成功创建了3.5D XDSiP平台。该平台通过垂直堆叠芯片元件,使芯片设计人员能够为每个元件选择最合适的制造工艺,同时缩小中介层和封装尺寸,从而显著提升性能、效率和成本效益。

台积电业务开发、全球业务资深副总经理兼副共同营运长张晓强也对这一合作表示了高度认可。他提到,在过去几年中,台积电与博通紧密携手,将台积电最先进的逻辑制程和3D芯片堆叠技术与博通的设计专长相结合。双方期待将这一平台产品化,以推动AI领域的创新和未来增长。

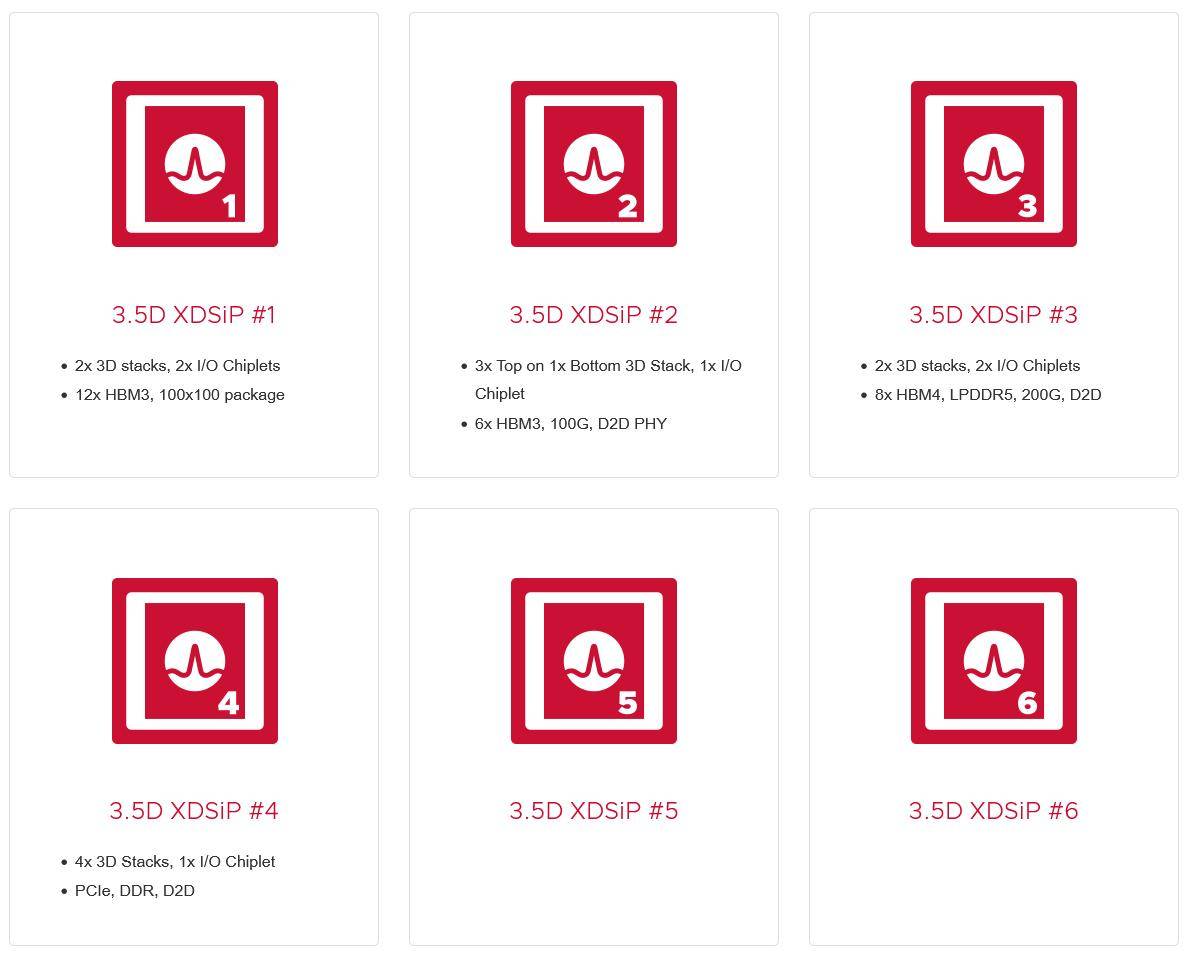

据博通透露,其大多数“消费级AI客户”已经采用了3.5D XDSiP平台技术,并且已有6款基于该平台的3.5D产品正在开发中,预计将于2026年2月开始生产出货。富士通已经明确表示将在其2nm制程Arm服务器处理器FUJITSU-MONAKA中采用这一平台。

在博通官网展示的六个3.5D XDSiP案例中,富士通的FUJITSU-MONAKA很可能对应其中之一。这一合作不仅展示了博通在3.5D封装技术方面的领先地位,也预示着未来AI芯片领域将更加依赖先进的封装技术来满足日益增长的性能需求。